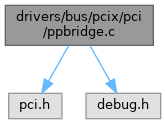

#include <pci.h>#include <debug.h>

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Macro Definition Documentation

◆ NDEBUG

| #define NDEBUG |

Definition at line 13 of file ppbridge.c.

Function Documentation

◆ PciBridgeIoBase()

| ULONG NTAPI PciBridgeIoBase | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 20 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings().

◆ PciBridgeIoLimit()

| ULONG NTAPI PciBridgeIoLimit | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 47 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings(), and PPBridge_SaveLimits().

◆ PciBridgeIsPositiveDecode()

| BOOLEAN NTAPI PciBridgeIsPositiveDecode | ( | IN PPCI_PDO_EXTENSION | PdoExtension | ) |

Definition at line 165 of file ppbridge.c.

Referenced by PciBridgeIsSubtractiveDecode().

◆ PciBridgeIsSubtractiveDecode()

| BOOLEAN NTAPI PciBridgeIsSubtractiveDecode | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 173 of file ppbridge.c.

Referenced by PPBridge_SaveLimits().

◆ PciBridgeMemoryBase()

| ULONG NTAPI PciBridgeMemoryBase | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 74 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings().

◆ PciBridgeMemoryLimit()

| ULONG NTAPI PciBridgeMemoryLimit | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 84 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings(), and PPBridge_SaveLimits().

◆ PciBridgeMemoryWorstCaseAlignment()

Definition at line 148 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings().

◆ PciBridgePrefetchMemoryBase()

| PHYSICAL_ADDRESS NTAPI PciBridgePrefetchMemoryBase | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 94 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings().

◆ PciBridgePrefetchMemoryLimit()

| PHYSICAL_ADDRESS NTAPI PciBridgePrefetchMemoryLimit | ( | IN PPCI_COMMON_HEADER | PciData | ) |

Definition at line 121 of file ppbridge.c.

Referenced by PPBridge_SaveCurrentSettings(), and PPBridge_SaveLimits().

◆ PPBridge_ChangeResourceSettings()

| VOID NTAPI PPBridge_ChangeResourceSettings | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 683 of file ppbridge.c.

◆ PPBridge_GetAdditionalResourceDescriptors()

| VOID NTAPI PPBridge_GetAdditionalResourceDescriptors | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context, |

| IN PPCI_COMMON_HEADER | PciData, | ||

| IN PIO_RESOURCE_DESCRIPTOR | IoDescriptor | ||

| ) |

Definition at line 628 of file ppbridge.c.

◆ PPBridge_MassageHeaderForLimitsDetermination()

| VOID NTAPI PPBridge_MassageHeaderForLimitsDetermination | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 582 of file ppbridge.c.

◆ PPBridge_ResetDevice()

| VOID NTAPI PPBridge_ResetDevice | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 673 of file ppbridge.c.

◆ PPBridge_RestoreCurrent()

| VOID NTAPI PPBridge_RestoreCurrent | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 620 of file ppbridge.c.

◆ PPBridge_SaveCurrentSettings()

| VOID NTAPI PPBridge_SaveCurrentSettings | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 225 of file ppbridge.c.

◆ PPBridge_SaveLimits()

| VOID NTAPI PPBridge_SaveLimits | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 465 of file ppbridge.c.