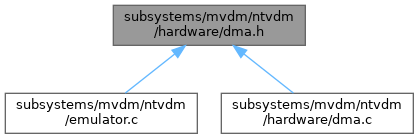

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | _DMA_CHANNEL |

| struct | _DMA_CONTROLLER |

| struct | _DMA_PAGE_REGISTER |

Macros | |

| #define | DMA_CONTROLLERS 2 |

| #define | DMA_CONTROLLER_CHANNELS 4 |

Typedefs | |

| typedef struct _DMA_CHANNEL | DMA_CHANNEL |

| typedef struct _DMA_CHANNEL * | PDMA_CHANNEL |

| typedef struct _DMA_CONTROLLER | DMA_CONTROLLER |

| typedef struct _DMA_CONTROLLER * | PDMA_CONTROLLER |

| typedef struct _DMA_PAGE_REGISTER | DMA_PAGE_REGISTER |

| typedef struct _DMA_PAGE_REGISTER * | PDMA_PAGE_REGISTER |

Functions | |

| DWORD | DmaRequest (IN WORD iChannel, IN OUT PVOID Buffer, IN DWORD length) |

| VOID | DmaInitialize (VOID) |

Macro Definition Documentation

◆ DMA_CONTROLLER_CHANNELS

◆ DMA_CONTROLLERS

Typedef Documentation

◆ DMA_CHANNEL

| typedef struct _DMA_CHANNEL DMA_CHANNEL |

◆ DMA_CONTROLLER

| typedef struct _DMA_CONTROLLER DMA_CONTROLLER |

◆ DMA_PAGE_REGISTER

◆ PDMA_CHANNEL

| typedef struct _DMA_CHANNEL * PDMA_CHANNEL |

◆ PDMA_CONTROLLER

| typedef struct _DMA_CONTROLLER * PDMA_CONTROLLER |

◆ PDMA_PAGE_REGISTER

| typedef struct _DMA_PAGE_REGISTER * PDMA_PAGE_REGISTER |

Function Documentation

◆ DmaInitialize()

Definition at line 549 of file dma.c.

550{

551 /* Register the I/O Ports */

552

553 /* Channels 0(Reserved)..3 */

554 RegisterIoPort(0x00, DmaReadPort, DmaWritePort); /* Current(R) / Start(W) Address Register 0 (Reserved) */

555 RegisterIoPort(0x01, DmaReadPort, DmaWritePort); /* Current(R) / Base (W) Count Register 0 (Reserved) */

562

563 RegisterIoPort(0x08, DmaReadPort, DmaWritePort); /* Status (Read) / Command (Write) Registers */

568 RegisterIoPort(0x0D, DmaReadPort, DmaWritePort); /* Intermediate (Read) / Master Reset (Write) Registers */

571

572

573 /* Channels 4(Reserved)..7 */

574 RegisterIoPort(0xC0, DmaReadPort, DmaWritePort); /* Current(R) / Start(W) Address Register 4 (Reserved) */

575 RegisterIoPort(0xC2, DmaReadPort, DmaWritePort); /* Current(R) / Base (W) Count Register 4 (Reserved) */

582

583 RegisterIoPort(0xD0, DmaReadPort, DmaWritePort); /* Status (Read) / Command (Write) Registers */

588 RegisterIoPort(0xDA, DmaReadPort, DmaWritePort); /* Intermediate (Read) / Master Reset (Write) Registers */

591

592

593 /* Channels Page Address Registers */

602}

VOID RegisterIoPort(USHORT Port, EMULATOR_INB_PROC InHandler, EMULATOR_OUTB_PROC OutHandler)

Definition: io.c:320

Referenced by EmulatorInitialize().

◆ DmaRequest()

Definition at line 386 of file dma.c.

389{

390/*

391 * NOTE: This function is adapted from Wine's krnl386.exe,

392 * DMA emulation by Christian Costa.

393 */

394 PDMA_CONTROLLER pDcp;

396

400

401 ULONG CurrAddress;

402

404 {

406 return 0;

407 }

408

411

413

415

416 /* Exit if the controller is disabled or the channel is masked */

418 return 0;

419

420 OpMode = (RegMode & 0xC0) >> 6;

421 Increment = !(RegMode & 0x20);

422 Autoinit = RegMode & 0x10;

423 TrMode = (RegMode & 0x0C) >> 2;

424

425 /* Process operating mode */

426 switch (OpMode)

427 {

428 case 0:

429 /* Request mode */

431 return 0;

432 case 1:

433 /* Single Mode */

434 break;

435 case 2:

436 /* Request mode */

438 return 0;

439 case 3:

440 /* Cascade Mode */

442 return 0;

443 }

444

445 /* Perform one the 4 transfer modes */

446 if (TrMode == 4)

447 {

448 /* Illegal */

450 return 0;

451 }

452

453 /* Transfer size : 8 bits for channels 0..3, 16 bits for channels 4..7 */

455

456 // FIXME: Handle wrapping?

457 /* Get the number of elements to transfer */

460

461 /* 16-bit mode addressing, see: https://wiki.osdev.org/ISA_DMA#16_bit_issues */

462 CurrAddress = (iChannel < 4) ? (DmaPageRegisters[iChannel].Page << 16) | ((pDcp->DmaChannel[Channel].CurrAddress << 0) & 0xFFFF)

463 : (DmaPageRegisters[iChannel].Page << 16) | ((pDcp->DmaChannel[Channel].CurrAddress << 1) & 0xFFFF);

464

465 switch (TrMode)

466 {

467 /* Verification (no real transfer) */

468 case 0:

469 {

471 break;

472 }

473

474 /* Write */

475 case 1:

476 {

479

481 {

483 }

484 else

485 {

487 {

489 }

490 }

491

492 break;

493 }

494

495 /* Read */

496 case 2:

497 {

500

502 {

504 }

505 else

506 {

508 {

510 }

511 }

512

513 break;

514 }

515 }

516

517 /* Update DMA registers */

521 else

523

524 /* Check for end of transfer */

526 {

528

529 /* Update status register of the DMA chip corresponding to the channel */

532

533 if (Autoinit)

534 {

535 /* Reload Current* registers to their initial values */

538 }

539 else

540 {

541 /* Set the mask bit for the channel */

543 }

544 }

545

547}

Definition: bufpool.h:45

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

Definition: dma.h:28

static DMA_PAGE_REGISTER DmaPageRegisters[DMA_CONTROLLERS *DMA_CONTROLLER_CHANNELS]

Definition: dma.c:32

VOID FASTCALL EmulatorReadMemory(PFAST486_STATE State, ULONG Address, PVOID Buffer, ULONG Size)

Definition: memory.c:142

VOID FASTCALL EmulatorWriteMemory(PFAST486_STATE State, ULONG Address, PVOID Buffer, ULONG Size)

Definition: memory.c:186

_Must_inspect_result_ _In_ WDFDEVICE _In_ PWDF_DEVICE_PROPERTY_DATA _In_ DEVPROPTYPE _In_ ULONG Size

Definition: wdfdevice.h:4539

Referenced by VDDRequestDMA().