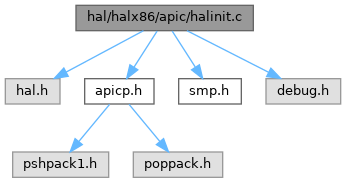

Include dependency graph for halinit.c:

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Functions | |

| VOID NTAPI | ApicInitializeLocalApic (ULONG Cpu) |

| VOID NTAPI | HalpInitProcessor (IN ULONG ProcessorNumber, IN PLOADER_PARAMETER_BLOCK LoaderBlock) |

| VOID | HalpInitPhase0 (IN PLOADER_PARAMETER_BLOCK LoaderBlock) |

| VOID | HalpInitPhase1 (VOID) |

Macro Definition Documentation

◆ NDEBUG

Function Documentation

◆ ApicInitializeLocalApic()

Definition at line 292 of file apic.c.

293{

294 APIC_BASE_ADDRESS_REGISTER BaseRegister;

295 APIC_SPURIOUS_INERRUPT_REGISTER SpIntRegister;

296 LVT_REGISTER LvtEntry;

297

298 /* Enable the APIC if it wasn't yet */

300 BaseRegister.Enable = 1;

301 BaseRegister.BootStrapCPUCore = (Cpu == 0);

303

304 /* Set spurious vector and SoftwareEnable to 1 */

307 SpIntRegister.SoftwareEnable = 1;

308 SpIntRegister.FocusCPUCoreChecking = 0;

310

311 /* Read the version and save it globally */

313

314 /* Set the mode to flat (max 8 CPUs supported!) */

316

317 /* Set logical apic ID */

319

320 /* Set the spurious ISR */

322

323 /* Create a template LVT */

324 LvtEntry.Long = 0;

327 LvtEntry.DeliveryStatus = 0;

328 LvtEntry.RemoteIRR = 0;

330 LvtEntry.Mask = 1;

331 LvtEntry.TimerMode = 0;

332

333 /* Initialize and mask LVTs */

341

342 /* LINT0 */

346

347 /* Enable LINT1 (NMI) */

348 LvtEntry.Mask = 0;

353

354 /* Enable error LVTR */

358

359 /* Set the IRQL from the PCR */

361#ifdef APIC_LAZY_IRQL

362 /* Save the new hard IRQL in the IRR field */

364#endif

365}

VOID __cdecl ApicSpuriousService(VOID)

FORCEINLINE VOID KeRegisterInterruptHandler(IN ULONG Vector, IN PVOID Handler)

Definition: ke.h:303

Definition: apicp.h:190

Definition: apicp.h:204

UINT32 FocusCPUCoreChecking

Definition: apicp.h:210

Definition: apicp.h:265

Referenced by HalpInitProcessor().

◆ HalpInitPhase0()

| VOID HalpInitPhase0 | ( | IN PLOADER_PARAMETER_BLOCK | LoaderBlock | ) |

Definition at line 46 of file halinit.c.

47{

51

52 HalpPrintApicTables();

53

54 /* Enable clock interrupt handler */

56 0,

58 CLOCK2_LEVEL,

60 Latched);

61

62 /* Enable profile interrupt handler */

64 0,

68 Latched);

69}

VOID NTAPI HalpEnableInterruptHandler(IN UCHAR Flags, IN ULONG BusVector, IN ULONG SystemVector, IN KIRQL Irql, IN PVOID Handler, IN KINTERRUPT_MODE Mode)

Definition: usage.c:49

VOID HalpProfileInterrupt(VOID)

◆ HalpInitPhase1()

◆ HalpInitProcessor()

Definition at line 24 of file halinit.c.

27{

28 if (ProcessorNumber == 0)

29 {

30 HalpParseApicTables(LoaderBlock);

31 }

32

33 HalpSetupProcessorsTable(ProcessorNumber);

34

35 /* Initialize the local APIC for this cpu */

36 ApicInitializeLocalApic(ProcessorNumber);

37

38 /* Initialize profiling data (but don't start it) */

39 HalInitializeProfiling();

40

41 /* Initialize the timer */

42 //ApicInitializeTimer(ProcessorNumber);

43}

VOID HalpParseApicTables(_In_ PLOADER_PARAMETER_BLOCK LoaderBlock)

Definition: madt.c:55

VOID HalpSetupProcessorsTable(_In_ UINT32 NTProcessorNumber)

Definition: up.c:37

Referenced by HalInitializeProcessor().