serial.h File Reference

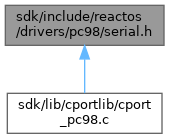

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macro Definition Documentation

◆ SER_8251A_REG_DATA

◆ SER_8251A_REG_STATUS

◆ SER_8251F_REG_DLR

◆ SER_8251F_REG_FCR

◆ SER_8251F_REG_IIR

◆ SER_8251F_REG_LSR

◆ SER_8251F_REG_MSR

◆ SER_8251F_REG_RBR

◆ SR_8251A_COMMMAND_DTR

◆ SR_8251A_COMMMAND_EH

◆ SR_8251A_COMMMAND_ER

◆ SR_8251A_COMMMAND_IR

◆ SR_8251A_COMMMAND_RTS

◆ SR_8251A_COMMMAND_RxEN

◆ SR_8251A_COMMMAND_SBRK

| #define SR_8251A_COMMMAND_SBRK 0x08 /* Send break character */ |

◆ SR_8251A_COMMMAND_TxEN

◆ SR_8251A_MODE_1_5_STOP

◆ SR_8251A_MODE_1_STOP

◆ SR_8251A_MODE_2_STOP

◆ SR_8251A_MODE_CLOCKx1

◆ SR_8251A_MODE_CLOCKx16

◆ SR_8251A_MODE_CLOCKx64

◆ SR_8251A_MODE_EP

| #define SR_8251A_MODE_EP 0x20 /* Even parity generation/check */ |

◆ SR_8251A_MODE_ESD

◆ SR_8251A_MODE_LENGTH_5

◆ SR_8251A_MODE_LENGTH_6

◆ SR_8251A_MODE_LENGTH_7

◆ SR_8251A_MODE_LENGTH_8

◆ SR_8251A_MODE_PEN

◆ SR_8251A_MODE_SCS

◆ SR_8251A_MODE_SYNC

◆ SR_8251A_STATUS_DSR

◆ SR_8251A_STATUS_FE

◆ SR_8251A_STATUS_OE

◆ SR_8251A_STATUS_PE

◆ SR_8251A_STATUS_RxRDY

◆ SR_8251A_STATUS_SYNDET

| #define SR_8251A_STATUS_SYNDET 0x40 /* Sync detect / Break detect */ |