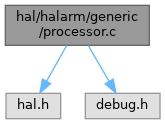

#include <hal.h>#include <debug.h>

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Functions | |

| VOID | HalpIdentifyProcessor (VOID) |

| VOID NTAPI | HalInitializeProcessor (IN ULONG ProcessorNumber, IN PLOADER_PARAMETER_BLOCK LoaderBlock) |

| BOOLEAN NTAPI | HalAllProcessorsStarted (VOID) |

| BOOLEAN NTAPI | HalStartNextProcessor (IN PLOADER_PARAMETER_BLOCK LoaderBlock, IN PKPROCESSOR_STATE ProcessorState) |

| VOID NTAPI | HalProcessorIdle (VOID) |

| VOID NTAPI | HalRequestIpi (KAFFINITY TargetProcessors) |

| VOID | HalSweepDcache (VOID) |

| VOID | HalSweepIcache (VOID) |

Variables | |

| KAFFINITY | HalpActiveProcessors |

| KAFFINITY | HalpDefaultInterruptAffinity |

| BOOLEAN | HalpProcessorIdentified |

| BOOLEAN | HalpTestCleanSupported |

Macro Definition Documentation

◆ NDEBUG

| #define NDEBUG |

Definition at line 12 of file processor.c.

Function Documentation

◆ HalAllProcessorsStarted()

Definition at line 60 of file processor.c.

Referenced by Phase1InitializationDiscard().

◆ HalInitializeProcessor()

| VOID NTAPI HalInitializeProcessor | ( | IN ULONG | ProcessorNumber, |

| IN PLOADER_PARAMETER_BLOCK | LoaderBlock | ||

| ) |

Definition at line 48 of file processor.c.

Referenced by KiInitializeSystem(), and KiSystemStartup().

◆ HalpIdentifyProcessor()

Definition at line 25 of file processor.c.

Referenced by HalSweepDcache().

◆ HalProcessorIdle()

Definition at line 83 of file processor.c.

Referenced by PopIdle0().

◆ HalRequestIpi()

Definition at line 96 of file processor.c.

◆ HalStartNextProcessor()

| BOOLEAN NTAPI HalStartNextProcessor | ( | IN PLOADER_PARAMETER_BLOCK | LoaderBlock, |

| IN PKPROCESSOR_STATE | ProcessorState | ||

| ) |

Definition at line 71 of file processor.c.

Referenced by KeStartAllProcessors().

◆ HalSweepDcache()

Definition at line 107 of file processor.c.

Referenced by KiInitializeKernel(), and KiInitializeSystem().

◆ HalSweepIcache()

Definition at line 135 of file processor.c.

Referenced by KiInitializeSystem().

Variable Documentation

◆ HalpActiveProcessors

| KAFFINITY HalpActiveProcessors |

Definition at line 17 of file processor.c.

Referenced by HalInitializeProcessor(), HalpBuildPartialFromIdt(), and HalRequestIpiSpecifyVector().

◆ HalpDefaultInterruptAffinity

| KAFFINITY HalpDefaultInterruptAffinity |

Definition at line 18 of file processor.c.

Referenced by HalInitializeProcessor(), and HalpGetRootInterruptVector().

◆ HalpProcessorIdentified

| BOOLEAN HalpProcessorIdentified |

Definition at line 19 of file processor.c.

Referenced by HalpIdentifyProcessor(), and HalSweepDcache().

◆ HalpTestCleanSupported

| BOOLEAN HalpTestCleanSupported |

Definition at line 20 of file processor.c.

Referenced by HalpIdentifyProcessor(), and HalSweepDcache().