#include <Cpuid.h>

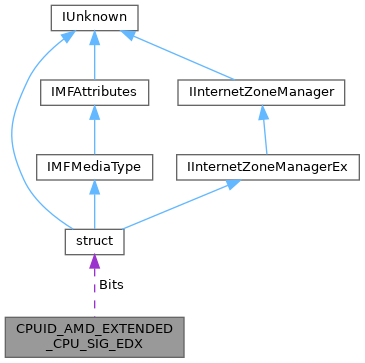

CPUID Extended Processor Signature and Features EDX for CPUID leaf CPUID_EXTENDED_CPU_SIG.

Definition at line 256 of file Cpuid.h.

◆ APIC

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::APIC |

[Bit 9] APIC exists and is enabled.

Definition at line 300 of file Cpuid.h.

| struct { ... } CPUID_AMD_EXTENDED_CPU_SIG_EDX::Bits |

◆ CMOV

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::CMOV |

[Bit 15] Conditional move instructions, CMOV, FCOMI, FCMOV.

Definition at line 324 of file Cpuid.h.

◆ CMPXCHG8B

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::CMPXCHG8B |

[Bit 8] CMPXCHG8B instruction.

Definition at line 296 of file Cpuid.h.

◆ DE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::DE |

[Bit 2] Debugging extensions, IO breakpoints, CR4.DE.

Definition at line 272 of file Cpuid.h.

◆ FFSR

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::FFSR |

[Bit 24] FXSAVE and FXRSTOR instructions.

Definition at line 356 of file Cpuid.h.

◆ FFXSR

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::FFXSR |

[Bit 25] FXSAVE and FXRSTOR instruction optimizations.

Definition at line 360 of file Cpuid.h.

◆ FPU

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::FPU |

[Bit 0] x87 floating point unit on-chip.

Definition at line 264 of file Cpuid.h.

◆ LM

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::LM |

[Bit 29] Long Mode.

Definition at line 376 of file Cpuid.h.

◆ MCA

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MCA |

[Bit 14] Machine check architecture, MCG_CAP.

Definition at line 320 of file Cpuid.h.

◆ MCE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MCE |

[Bit 7] Machine check exception, CR4.MCE.

Definition at line 292 of file Cpuid.h.

◆ MMX

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MMX |

[Bit 23] MMX instructions.

Definition at line 352 of file Cpuid.h.

◆ MmxExt

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MmxExt |

◆ MSR

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MSR |

[Bit 5] MSRs, with RDMSR and WRMSR instructions.

Definition at line 284 of file Cpuid.h.

◆ MTRR

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::MTRR |

[Bit 12] Memory-type range registers.

Definition at line 312 of file Cpuid.h.

◆ NX

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::NX |

[Bit 20] No-execute page protection.

Definition at line 340 of file Cpuid.h.

◆ PAE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::PAE |

[Bit 6] Physical-address extensions (PAE).

Definition at line 288 of file Cpuid.h.

◆ Page1GB

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Page1GB |

[Bit 26] 1-GByte large page support.

Definition at line 364 of file Cpuid.h.

◆ PAT

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::PAT |

[Bit 16] Page attribute table.

Definition at line 328 of file Cpuid.h.

◆ PGE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::PGE |

[Bit 13] Page global extension, CR4.PGE.

Definition at line 316 of file Cpuid.h.

◆ PSE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::PSE |

[Bit 3] Page-size extensions (4 MB pages).

Definition at line 276 of file Cpuid.h.

◆ PSE36

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::PSE36 |

[Bit 17] Page-size extensions.

Definition at line 332 of file Cpuid.h.

◆ RDTSCP

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::RDTSCP |

[Bit 27] RDTSCP instructions.

Definition at line 368 of file Cpuid.h.

◆ Reserved1

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Reserved1 |

[Bit 10] Reserved.

Definition at line 304 of file Cpuid.h.

◆ Reserved2

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Reserved2 |

[Bit 19:18] Reserved.

Definition at line 336 of file Cpuid.h.

◆ Reserved3

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Reserved3 |

[Bit 21] Reserved.

Definition at line 344 of file Cpuid.h.

◆ Reserved4

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Reserved4 |

[Bit 28] Reserved.

Definition at line 372 of file Cpuid.h.

◆ SYSCALL_SYSRET

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::SYSCALL_SYSRET |

[Bit 11] SYSCALL and SYSRET instructions.

Definition at line 308 of file Cpuid.h.

◆ ThreeDNow

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::ThreeDNow |

[Bit 30] 3DNow! instructions.

Definition at line 380 of file Cpuid.h.

◆ ThreeDNowExt

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::ThreeDNowExt |

◆ TSC

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::TSC |

[Bit 4] Time stamp counter, RDTSC/RDTSCP instructions, CR4.TSD.

Definition at line 280 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::Uint32 |

All bit fields as a 32-bit value

Definition at line 389 of file Cpuid.h.

◆ VME

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_EDX::VME |

[Bit 1] Virtual-mode enhancements.

Definition at line 268 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Amd/Cpuid.h