#include <Cpuid.h>

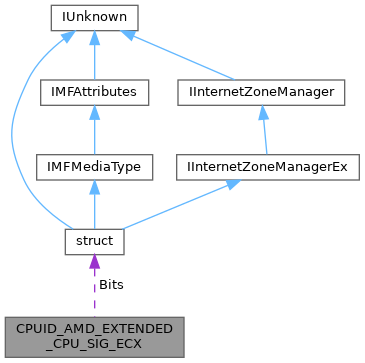

CPUID Extended Processor Signature and Features ECX for CPUID leaf CPUID_EXTENDED_CPU_SIG.

Definition at line 132 of file Cpuid.h.

◆ AltMovCr8

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::AltMovCr8 |

[Bit 4] LOCK MOV CR0 means MOV CR8.

Definition at line 156 of file Cpuid.h.

| struct { ... } CPUID_AMD_EXTENDED_CPU_SIG_ECX::Bits |

◆ CmpLegacy

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::CmpLegacy |

[Bit 1] Core multi-processing legacy mode.

Definition at line 144 of file Cpuid.h.

◆ DataBreakpointExtension

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::DataBreakpointExtension |

[Bit 26] Data Breakpoint Extension.

Definition at line 228 of file Cpuid.h.

◆ ExtApicSpace

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::ExtApicSpace |

[Bit 3] Extended APIC register space.

Definition at line 152 of file Cpuid.h.

◆ FMA4

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::FMA4 |

[Bit 16] 4-Operand FMA instruction support.

Definition at line 204 of file Cpuid.h.

◆ IBS

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::IBS |

[Bit 10] Instruction Based Sampling.

Definition at line 180 of file Cpuid.h.

◆ LAHF_SAHF

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::LAHF_SAHF |

[Bit 0] LAHF/SAHF available in 64-bit mode.

Definition at line 140 of file Cpuid.h.

◆ LWP

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::LWP |

[Bit 15] Lightweight Profiling support.

Definition at line 200 of file Cpuid.h.

◆ LZCNT

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::LZCNT |

[Bit 5] LZCNT instruction support.

Definition at line 160 of file Cpuid.h.

◆ MisAlignSse

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::MisAlignSse |

[Bit 7] Misaligned SSE Mode.

Definition at line 168 of file Cpuid.h.

◆ MwaitExtended

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::MwaitExtended |

[Bit 29] MWAITX and MONITORX capability.

Definition at line 240 of file Cpuid.h.

◆ OSVW

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::OSVW |

[Bit 9] OS Visible Work-around support.

Definition at line 176 of file Cpuid.h.

◆ PerfCtrExtCore

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::PerfCtrExtCore |

◆ PerfCtrExtL3

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::PerfCtrExtL3 |

◆ PerfTsc

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::PerfTsc |

[Bit 27] Performance Time-Stamp Counter.

Definition at line 232 of file Cpuid.h.

◆ PREFETCHW

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::PREFETCHW |

[Bit 8] ThreeDNow Prefetch instructions.

Definition at line 172 of file Cpuid.h.

◆ Reserved1

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::Reserved1 |

[Bit 14] Reserved.

Definition at line 196 of file Cpuid.h.

◆ Reserved2

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::Reserved2 |

[Bit 21:18] Reserved.

Definition at line 212 of file Cpuid.h.

◆ Reserved3

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::Reserved3 |

[Bit 25:24] Reserved.

Definition at line 224 of file Cpuid.h.

◆ Reserved4

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::Reserved4 |

[Bit 31:30] Reserved.

Definition at line 244 of file Cpuid.h.

◆ SKINIT

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::SKINIT |

[Bit 12] SKINIT and STGI support.

Definition at line 188 of file Cpuid.h.

◆ SSE4A

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::SSE4A |

[Bit 6] SSE4A instruction support.

Definition at line 164 of file Cpuid.h.

◆ SVM

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::SVM |

[Bit 2] Secure Virtual Mode feature.

Definition at line 148 of file Cpuid.h.

◆ TCE

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::TCE |

[Bit 17] Translation Cache Extension.

Definition at line 208 of file Cpuid.h.

◆ TopologyExtensions

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::TopologyExtensions |

◆ Uint32

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::Uint32 |

All bit fields as a 32-bit value

Definition at line 249 of file Cpuid.h.

◆ WDT

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::WDT |

◆ XOP

| UINT32 CPUID_AMD_EXTENDED_CPU_SIG_ECX::XOP |

[Bit 11] Extended Operation Support.

Definition at line 184 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Amd/Cpuid.h