#include <Cpuid.h>

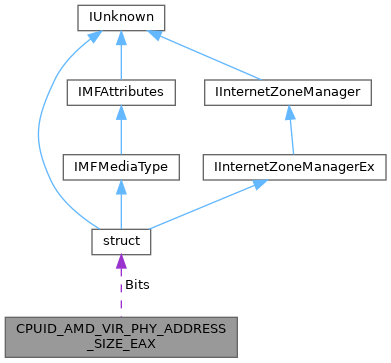

CPUID Linear Physical Address Size

- Parameters

-

| EAX | CPUID_VIR_PHY_ADDRESS_SIZE (0x80000008) |

- Return values

-

Definition at line 410 of file Cpuid.h.

| struct { ... } CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::Bits |

◆ GuestPhysAddrSize

| UINT32 CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::GuestPhysAddrSize |

[Bits 23:16] Maximum guest physical byte address size in bits.

Definition at line 426 of file Cpuid.h.

◆ LinearAddressBits

| UINT32 CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::LinearAddressBits |

[Bits 15:8] Maximum linear byte address size in bits.

Definition at line 422 of file Cpuid.h.

◆ PhysicalAddressBits

| UINT32 CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::PhysicalAddressBits |

[Bits 7:0] Maximum physical byte address size in bits.

Definition at line 418 of file Cpuid.h.

◆ Reserved

| UINT32 CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::Reserved |

[Bit 31:24] Reserved.

Definition at line 430 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_AMD_VIR_PHY_ADDRESS_SIZE_EAX::Uint32 |

All bit fields as a 32-bit value

Definition at line 435 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Amd/Cpuid.h