#include <ntdef.h>#include <dderror.h>#include <miniport.h>#include <video.h>#include "cmdcnst.h"#include "vbe.h"

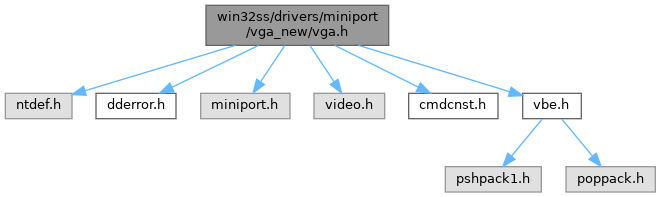

Include dependency graph for vga.h:

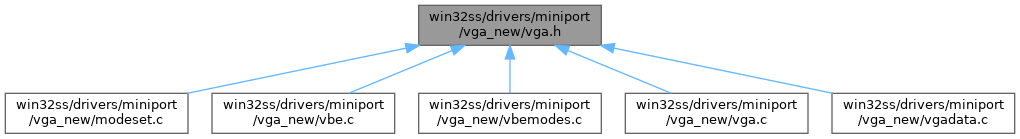

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | VIDEOMODE |

| struct | _VGA_VALIDATOR_DATA |

| struct | _HW_DEVICE_EXTENSION |

Typedefs | |

| typedef struct VIDEOMODE * | PVIDEOMODE |

| typedef struct _VGA_VALIDATOR_DATA | VGA_VALIDATOR_DATA |

| typedef struct _VGA_VALIDATOR_DATA * | PVGA_VALIDATOR_DATA |

| typedef struct _HW_DEVICE_EXTENSION | HW_DEVICE_EXTENSION |

| typedef struct _HW_DEVICE_EXTENSION * | PHW_DEVICE_EXTENSION |

Variables | |

| USHORT | EnableA000Data [] |

| USHORT | DisableA000Color [] |

| ULONG | NumVideoModes |

| VIDEOMODE | ModesVGA [] |

| PVIDEOMODE | VgaModeList |

| VIDEO_ACCESS_RANGE | VgaAccessRange [] |

Macro Definition Documentation

◆ ATT_ADDRESS_OFFSET

◆ ATT_ADDRESS_PORT

◆ ATT_DATA_READ_PORT

◆ ATT_DATA_WRITE_PORT

◆ ATT_INITIALIZE_PORT_COLOR

| #define ATT_INITIALIZE_PORT_COLOR INPUT_STATUS_1_COLOR |

◆ ATT_INITIALIZE_PORT_MONO

| #define ATT_INITIALIZE_PORT_MONO INPUT_STATUS_1_MONO |

◆ BIT_MASK_DEFAULT

◆ CAPS_BLT_SUPPORT

◆ CAPS_CURSOR_VERT_EXP

◆ CAPS_IS_542x

◆ CAPS_IS_5436

◆ CAPS_MM_IO

◆ CAPS_NO_HOST_XFER

◆ CAPS_SW_POINTER

◆ CAPS_TRUE_COLOR

◆ CHAIN4_MASK

◆ CL6340_ENABLE_READBACK_ALLSEL_VALUE

◆ CL6340_ENABLE_READBACK_OFF_VALUE

◆ CL6340_ENABLE_READBACK_REGISTER

◆ CL6340_IDENTIFICATION_REGISTER

◆ CL64xx_EXTENSION_DISABLE_VALUE

◆ CL64xx_EXTENSION_ENABLE_INDEX

◆ CL64xx_EXTENSION_ENABLE_VALUE

◆ CL64xx_TRISTATE_CONTROL_REG

◆ CRTC_ADDRESS_COLOR_OFFSET

◆ CRTC_ADDRESS_MONO_OFFSET

◆ CRTC_ADDRESS_PORT_COLOR

◆ CRTC_ADDRESS_PORT_MONO

◆ CRTC_DATA_PORT_COLOR

◆ CRTC_DATA_PORT_MONO

◆ DAC_ADDRESS_READ_PORT

◆ DAC_ADDRESS_WRITE_OFFSET

◆ DAC_ADDRESS_WRITE_PORT

◆ DAC_DATA_REG_PORT

◆ DAC_PIXEL_MASK_OFFSET

◆ DAC_PIXEL_MASK_PORT

◆ DAC_STATE_OFFSET

◆ DAC_STATE_PORT

◆ DEFAULT_MODE

◆ END_SYNC_RESET_VALUE

◆ EXT_NUM_ATTRIB_CONT_PORTS

◆ EXT_NUM_CRTC_PORTS

◆ EXT_NUM_DAC_ENTRIES

◆ EXT_NUM_GRAPH_CONT_PORTS

◆ EXT_NUM_SEQUENCER_PORTS

◆ FEAT_CTRL_READ_PORT

◆ FEAT_CTRL_WRITE_COLOR_OFFSET

◆ FEAT_CTRL_WRITE_MONO_OFFSET

◆ FEAT_CTRL_WRITE_PORT_COLOR

◆ FEAT_CTRL_WRITE_PORT_MONO

◆ GRAPH_ADDR_MASK

◆ GRAPH_ADDRESS_OFFSET

◆ GRAPH_ADDRESS_PORT

◆ GRAPH_DATA_PORT

◆ IND_ALP_SCRATCH_PAD

◆ IND_BIT_MASK

◆ IND_CL_EXTS_ENB

◆ IND_CL_ID_REG

◆ IND_CL_REV_REG

◆ IND_CL_SCRATCH_PAD

◆ IND_CR2C

◆ IND_CR2D

◆ IND_CRTC_COMPAT

◆ IND_CRTC_PROTECT

◆ IND_CURSOR_END

◆ IND_CURSOR_HIGH_LOC

◆ IND_CURSOR_LOW_LOC

◆ IND_CURSOR_START

◆ IND_DATA_ROTATE

◆ IND_GRAPH_MISC

◆ IND_GRAPH_MODE

◆ IND_MAP_MASK

◆ IND_MEMORY_MODE

◆ IND_NORD_SCRATCH_PAD

◆ IND_PERF_TUNING

◆ IND_READ_MAP

◆ IND_SET_RESET_ENABLE

◆ IND_SYNC_RESET

◆ IND_VSYNC_END

◆ INDEX_ENABLE_AUTO_START

◆ INPUT_STATUS_0_PORT

◆ INPUT_STATUS_1_COLOR

◆ INPUT_STATUS_1_MONO

◆ MEM_VGA

◆ MEM_VGA_SIZE

◆ MEMORY_MAPPED_IO_OFFSET

◆ MEMORY_MODE_TEXT_DEFAULT

◆ MISC_OUTPUT_REG_READ_PORT

◆ MISC_OUTPUT_REG_WRITE_OFFSET

◆ MISC_OUTPUT_REG_WRITE_PORT

◆ NUM_VGA_ACCESS_RANGES

◆ READ_MAP_DEFAULT

◆ READ_MAP_TEST_SETTING

◆ SEQ_ADDR_MASK

◆ SEQ_ADDRESS_OFFSET

◆ SEQ_ADDRESS_PORT

◆ SEQ_DATA_PORT

◆ START_SYNC_RESET_VALUE

◆ VESA_MAGIC

◆ VGA_BASE_IO_PORT

◆ VGA_BASIC_ATTRIB_CONT_OFFSET

| #define VGA_BASIC_ATTRIB_CONT_OFFSET |

Value:

◆ VGA_BASIC_CRTC_OFFSET

| #define VGA_BASIC_CRTC_OFFSET |

Value:

◆ VGA_BASIC_DAC_OFFSET

| #define VGA_BASIC_DAC_OFFSET |

Value:

◆ VGA_BASIC_GRAPH_CONT_OFFSET

| #define VGA_BASIC_GRAPH_CONT_OFFSET |

Value:

◆ VGA_BASIC_LATCHES_OFFSET

| #define VGA_BASIC_LATCHES_OFFSET |

Value:

(VGA_BASIC_DAC_OFFSET + \

(3 * VGA_NUM_DAC_ENTRIES))

◆ VGA_BASIC_SEQUENCER_OFFSET

| #define VGA_BASIC_SEQUENCER_OFFSET (VGA_HARDWARE_STATE_SIZE + 0) |

◆ VGA_END_BREAK_PORT

◆ VGA_EXT_ATTRIB_CONT_OFFSET

| #define VGA_EXT_ATTRIB_CONT_OFFSET |

Value:

◆ VGA_EXT_CRTC_OFFSET

| #define VGA_EXT_CRTC_OFFSET |

Value:

◆ VGA_EXT_DAC_OFFSET

| #define VGA_EXT_DAC_OFFSET |

Value:

◆ VGA_EXT_GRAPH_CONT_OFFSET

| #define VGA_EXT_GRAPH_CONT_OFFSET |

Value:

(VGA_EXT_CRTC_OFFSET + \

◆ VGA_EXT_SEQUENCER_OFFSET

| #define VGA_EXT_SEQUENCER_OFFSET (VGA_BASIC_LATCHES_OFFSET + 4) |

◆ VGA_HARDWARE_STATE_SIZE

| #define VGA_HARDWARE_STATE_SIZE sizeof(VIDEO_HARDWARE_STATE_HEADER) |

◆ VGA_MAX_IO_PORT

◆ VGA_MAX_VALIDATOR_DATA

◆ VGA_MISC_DATA_AREA_OFFSET

| #define VGA_MISC_DATA_AREA_OFFSET VGA_VALIDATOR_OFFSET + VGA_VALIDATOR_AREA_SIZE |

◆ VGA_MISC_DATA_AREA_SIZE

◆ VGA_NUM_ATTRIB_CONT_PORTS

◆ VGA_NUM_CRTC_PORTS

◆ VGA_NUM_DAC_ENTRIES

◆ VGA_NUM_GRAPH_CONT_PORTS

◆ VGA_NUM_SEQUENCER_PORTS

◆ VGA_PLANE_0_OFFSET

| #define VGA_PLANE_0_OFFSET VGA_MISC_DATA_AREA_OFFSET + VGA_MISC_DATA_AREA_SIZE |

◆ VGA_PLANE_1_OFFSET

| #define VGA_PLANE_1_OFFSET VGA_PLANE_0_OFFSET + VGA_PLANE_SIZE |

◆ VGA_PLANE_2_OFFSET

| #define VGA_PLANE_2_OFFSET VGA_PLANE_1_OFFSET + VGA_PLANE_SIZE |

◆ VGA_PLANE_3_OFFSET

| #define VGA_PLANE_3_OFFSET VGA_PLANE_2_OFFSET + VGA_PLANE_SIZE |

◆ VGA_PLANE_SIZE

◆ VGA_START_BREAK_PORT

◆ VGA_TOTAL_STATE_SIZE

| #define VGA_TOTAL_STATE_SIZE VGA_PLANE_3_OFFSET + VGA_PLANE_SIZE |

◆ VGA_VALIDATOR_AREA_SIZE

| #define VGA_VALIDATOR_AREA_SIZE |

Value:

sizeof (VGA_VALIDATOR_DATA)) + \

sizeof (ULONG) + \

sizeof (ULONG) + \

sizeof (PVIDEO_ACCESS_RANGE)

Definition: vga.h:301

Definition: video.h:214

◆ VGA_VALIDATOR_OFFSET

| #define VGA_VALIDATOR_OFFSET (VGA_EXT_DAC_OFFSET + 4 * EXT_NUM_DAC_ENTRIES) |

◆ VGA_VALIDATOR_UCHAR_ACCESS

◆ VGA_VALIDATOR_ULONG_ACCESS

◆ VGA_VALIDATOR_USHORT_ACCESS

◆ VIDEO_DISABLE

◆ VIDEO_ENABLE

◆ VIDEO_MAX_COLOR_REGISTER

◆ VIDEO_MAX_PALETTE_REGISTER

◆ VIDEO_SUBSYSTEM_ENABLE_OFFSET

◆ VIDEO_SUBSYSTEM_ENABLE_PORT

Typedef Documentation

◆ HW_DEVICE_EXTENSION

◆ PHW_DEVICE_EXTENSION

| typedef struct _HW_DEVICE_EXTENSION * PHW_DEVICE_EXTENSION |

◆ PVGA_VALIDATOR_DATA

| typedef struct _VGA_VALIDATOR_DATA * PVGA_VALIDATOR_DATA |

◆ PVIDEOMODE

| typedef struct VIDEOMODE * PVIDEOMODE |

◆ VGA_VALIDATOR_DATA

Variable Documentation

◆ DisableA000Color

|

extern |

Definition at line 473 of file vgadata.c.

Referenced by VgaZeroVideoMemory().

◆ EnableA000Data

|

extern |

Definition at line 447 of file vgadata.c.

Referenced by VgaZeroVideoMemory().

◆ ModesVGA

|

extern |

Definition at line 281 of file vgadata.c.

Referenced by InitializeModeTable().

◆ NumVideoModes

|

extern |

Definition at line 433 of file vgadata.c.

Referenced by InitializeModeTable(), VgaQueryAvailableModes(), VgaQueryNumberOfAvailableModes(), and VgaSetMode().

◆ VgaAccessRange

|

extern |

Definition at line 16 of file vgadata.c.

Referenced by VgaAcquireResources(), VgaFindAdapter(), and VgaStartIO().

◆ VgaModeList

|

extern |

Definition at line 434 of file vgadata.c.

Referenced by InitializeModeTable(), VgaQueryAvailableModes(), and VgaSetMode().