#include <iotypes.h>

Definition at line 4805 of file iotypes.h.

◆ AdditionalCorrectableError

| ULONG _PCIX_BRIDGE_CAPABILITY::AdditionalCorrectableError |

◆ AdditionalUncorrectableError

| ULONG _PCIX_BRIDGE_CAPABILITY::AdditionalUncorrectableError |

◆ AsULONG

| ULONG _PCIX_BRIDGE_CAPABILITY::AsULONG |

◆ AsUSHORT

| USHORT _PCIX_BRIDGE_CAPABILITY::AsUSHORT |

| union { ... } _PCIX_BRIDGE_CAPABILITY::BridgeStatus |

◆ Bus133MHzCapable

| USHORT _PCIX_BRIDGE_CAPABILITY::Bus133MHzCapable |

◆ Bus266MHzCapable

| USHORT _PCIX_BRIDGE_CAPABILITY::Bus266MHzCapable |

◆ Bus533MHzCapable

| USHORT _PCIX_BRIDGE_CAPABILITY::Bus533MHzCapable |

◆ Bus64Bit

| USHORT _PCIX_BRIDGE_CAPABILITY::Bus64Bit |

◆ BusModeFrequency

| USHORT _PCIX_BRIDGE_CAPABILITY::BusModeFrequency |

◆ BusNumber

| ULONG _PCIX_BRIDGE_CAPABILITY::BusNumber |

◆ ControlUpdateEnable

| ULONG _PCIX_BRIDGE_CAPABILITY::ControlUpdateEnable |

◆ Device133MHzCapable

| ULONG _PCIX_BRIDGE_CAPABILITY::Device133MHzCapable |

◆ Device266MHzCapable

| ULONG _PCIX_BRIDGE_CAPABILITY::Device266MHzCapable |

◆ Device533MHzCapable

| ULONG _PCIX_BRIDGE_CAPABILITY::Device533MHzCapable |

◆ Device64Bit

| ULONG _PCIX_BRIDGE_CAPABILITY::Device64Bit |

◆ DeviceNumber

| ULONG _PCIX_BRIDGE_CAPABILITY::DeviceNumber |

◆ DIMCapable

| ULONG _PCIX_BRIDGE_CAPABILITY::DIMCapable |

◆ DisableSingleBitCorrection

| ULONG _PCIX_BRIDGE_CAPABILITY::DisableSingleBitCorrection |

◆ DownstreamSplitTransactionCapacity

| USHORT _PCIX_BRIDGE_CAPABILITY::DownstreamSplitTransactionCapacity |

◆ DownstreamSplitTransactionLimit

| USHORT _PCIX_BRIDGE_CAPABILITY::DownstreamSplitTransactionLimit |

◆ [1/3]

| _ANONYMOUS_STRUCT struct { ... } _PCIX_BRIDGE_CAPABILITY::DUMMYSTRUCTNAME |

◆ [2/3]

| _ANONYMOUS_STRUCT struct { ... } _PCIX_BRIDGE_CAPABILITY::DUMMYSTRUCTNAME |

◆ [3/3]

| _ANONYMOUS_STRUCT struct { ... } _PCIX_BRIDGE_CAPABILITY::DUMMYSTRUCTNAME |

◆ EccAttribute

| ULONG _PCIX_BRIDGE_CAPABILITY::EccAttribute |

| union { ... } _PCIX_BRIDGE_CAPABILITY::EccControlStatus |

◆ EccFirstAddress

| ULONG _PCIX_BRIDGE_CAPABILITY::EccFirstAddress |

◆ EccMode

| ULONG _PCIX_BRIDGE_CAPABILITY::EccMode |

◆ EccSecondAddress

| ULONG _PCIX_BRIDGE_CAPABILITY::EccSecondAddress |

◆ ErrorCorrected

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorCorrected |

◆ ErrorFirstCommand

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorFirstCommand |

◆ ErrorPhase

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorPhase |

◆ ErrorPresentInOtherBank

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorPresentInOtherBank |

◆ ErrorSecondCommand

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorSecondCommand |

◆ ErrorUpperAttributes

| ULONG _PCIX_BRIDGE_CAPABILITY::ErrorUpperAttributes |

◆ FunctionNumber

| ULONG _PCIX_BRIDGE_CAPABILITY::FunctionNumber |

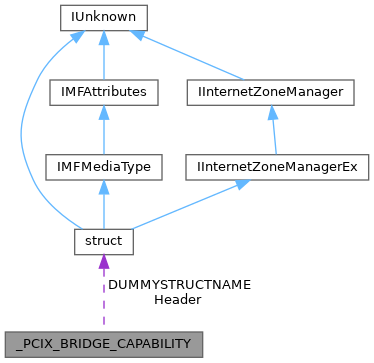

◆ Header

◆ Rsvd [1/2]

| USHORT _PCIX_BRIDGE_CAPABILITY::Rsvd |

◆ Rsvd [2/2]

| ULONG _PCIX_BRIDGE_CAPABILITY::Rsvd |

| union { ... } _PCIX_BRIDGE_CAPABILITY::SecondaryStatus |

◆ SelectSecondaryRegisters

| ULONG _PCIX_BRIDGE_CAPABILITY::SelectSecondaryRegisters |

◆ SplitCompletionDiscarded [1/2]

| USHORT _PCIX_BRIDGE_CAPABILITY::SplitCompletionDiscarded |

◆ SplitCompletionDiscarded [2/2]

| ULONG _PCIX_BRIDGE_CAPABILITY::SplitCompletionDiscarded |

◆ SplitCompletionOverrun [1/2]

| USHORT _PCIX_BRIDGE_CAPABILITY::SplitCompletionOverrun |

◆ SplitCompletionOverrun [2/2]

| ULONG _PCIX_BRIDGE_CAPABILITY::SplitCompletionOverrun |

◆ SplitRequestDelayed [1/2]

| USHORT _PCIX_BRIDGE_CAPABILITY::SplitRequestDelayed |

◆ SplitRequestDelayed [2/2]

| ULONG _PCIX_BRIDGE_CAPABILITY::SplitRequestDelayed |

◆ Syndrome

| ULONG _PCIX_BRIDGE_CAPABILITY::Syndrome |

◆ UnexpectedSplitCompletion [1/2]

| USHORT _PCIX_BRIDGE_CAPABILITY::UnexpectedSplitCompletion |

◆ UnexpectedSplitCompletion [2/2]

| ULONG _PCIX_BRIDGE_CAPABILITY::UnexpectedSplitCompletion |

◆ UpstreamSplitTransactionCapacity

| USHORT _PCIX_BRIDGE_CAPABILITY::UpstreamSplitTransactionCapacity |

◆ UpstreamSplitTransactionLimit

| USHORT _PCIX_BRIDGE_CAPABILITY::UpstreamSplitTransactionLimit |

◆ Version

| USHORT _PCIX_BRIDGE_CAPABILITY::Version |

The documentation for this struct was generated from the following file: