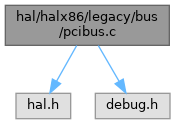

#include <hal.h>#include <debug.h>

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Macro Definition Documentation

◆ NDEBUG

Function Documentation

◆ HaliPciInterfaceReadConfig()

| ULONG NTAPI HaliPciInterfaceReadConfig | ( | IN PBUS_HANDLER | RootBusHandler, |

| IN ULONG | BusNumber, | ||

| IN PCI_SLOT_NUMBER | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 934 of file pcibus.c.

Referenced by HalpInitializePciStubs().

◆ HalpAdjustPCIResourceList()

| NTSTATUS NTAPI HalpAdjustPCIResourceList | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN OUT PIO_RESOURCE_REQUIREMENTS_LIST * | pResourceList | ||

| ) |

Definition at line 757 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler().

◆ HalpAssignPCISlotResources()

| NTSTATUS NTAPI HalpAssignPCISlotResources | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN PUNICODE_STRING | RegistryPath, | ||

| IN PUNICODE_STRING DriverClassName | OPTIONAL, | ||

| IN PDRIVER_OBJECT | DriverObject, | ||

| IN PDEVICE_OBJECT DeviceObject | OPTIONAL, | ||

| IN ULONG | Slot, | ||

| IN OUT PCM_RESOURCE_LIST * | AllocatedResources | ||

| ) |

Definition at line 798 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), and HalpAssignSlotResources().

◆ HalpGetISAFixedPCIIrq()

| NTSTATUS NTAPI HalpGetISAFixedPCIIrq | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN PCI_SLOT_NUMBER | PciSlot, | ||

| OUT PSUPPORTED_RANGE * | Range | ||

| ) |

Definition at line 702 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler().

◆ HalpGetPCIData()

| ULONG NTAPI HalpGetPCIData | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 507 of file pcibus.c.

Referenced by HalGetBusDataByOffset(), and HalpAllocateAndInitPciBusHandler().

◆ HalpGetPCIIntOnISABus()

| ULONG NTAPI HalpGetPCIIntOnISABus | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN ULONG | BusInterruptLevel, | ||

| IN ULONG | BusInterruptVector, | ||

| OUT PKIRQL | Irql, | ||

| OUT PKAFFINITY | Affinity | ||

| ) |

Definition at line 658 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler().

◆ HalpInitializePciStubs()

Definition at line 1190 of file pcibus.c.

Referenced by HalpInitializePciBus(), HalReportResourceUsage(), and LoadBootDeviceDriver().

◆ HalpPCIConfig()

| VOID NTAPI HalpPCIConfig | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| IN PUCHAR | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length, | ||

| IN FncConfigIO * | ConfigIO | ||

| ) |

Definition at line 219 of file pcibus.c.

Referenced by HalpReadPCIConfig(), and HalpWritePCIConfig().

◆ HalpPCIISALine2Pin()

| VOID NTAPI HalpPCIISALine2Pin | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN PCI_SLOT_NUMBER | SlotNumber, | ||

| IN PPCI_COMMON_CONFIG | PciNewData, | ||

| IN PPCI_COMMON_CONFIG | PciOldData | ||

| ) |

Definition at line 690 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler().

◆ HalpPCIPin2ISALine()

| VOID NTAPI HalpPCIPin2ISALine | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN PCI_SLOT_NUMBER | SlotNumber, | ||

| IN PPCI_COMMON_CONFIG | PciData | ||

| ) |

Definition at line 680 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler().

◆ HalpPCIReleaseSynchronizationType2()

Definition at line 193 of file pcibus.c.

◆ HalpPCIReleaseSynchronzationType1()

Definition at line 137 of file pcibus.c.

◆ HalpPCISynchronizeType1()

| VOID NTAPI HalpPCISynchronizeType1 | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| OUT PKIRQL | OldIrql, | ||

| OUT PPCI_TYPE1_CFG_BITS | PciCfg1 | ||

| ) |

Definition at line 118 of file pcibus.c.

◆ HalpPCISynchronizeType2()

| VOID NTAPI HalpPCISynchronizeType2 | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| OUT PKIRQL | OldIrql, | ||

| OUT PPCI_TYPE2_ADDRESS_BITS | PciCfg | ||

| ) |

Definition at line 162 of file pcibus.c.

◆ HalpPhase0GetPciDataByOffset()

| ULONG HalpPhase0GetPciDataByOffset | ( | _In_ ULONG | Bus, |

| _In_ PCI_SLOT_NUMBER | PciSlot, | ||

| _Out_writes_bytes_all_(Length) PVOID | Buffer, | ||

| _In_ ULONG | Offset, | ||

| _In_ ULONG | Length | ||

| ) |

Definition at line 368 of file pcibus.c.

Referenced by HalpConfigureDebuggingDevice(), and HalpFindMatchingDebuggingDevice().

◆ HalpPhase0SetPciDataByOffset()

| ULONG HalpPhase0SetPciDataByOffset | ( | _In_ ULONG | Bus, |

| _In_ PCI_SLOT_NUMBER | PciSlot, | ||

| _In_reads_bytes_(Length) PVOID | Buffer, | ||

| _In_ ULONG | Offset, | ||

| _In_ ULONG | Length | ||

| ) |

Definition at line 437 of file pcibus.c.

Referenced by HalpConfigureDebuggingDevice().

◆ HalpQueryPciRegistryInfo()

| PPCI_REGISTRY_INFO_INTERNAL NTAPI HalpQueryPciRegistryInfo | ( | VOID | ) |

Definition at line 957 of file pcibus.c.

Referenced by HalpInitializePciBus(), and HalpInitializePciStubs().

◆ HalpReadPCIConfig()

| VOID NTAPI HalpReadPCIConfig | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 257 of file pcibus.c.

Referenced by HaliPciInterfaceReadConfig(), HalpAllocateAndInitPciBusHandler(), HalpAssignPCISlotResources(), HalpDebugPciDumpBus(), HalpGetPciBridgeConfig(), HalpGetPCIData(), HalpInitializePciBus(), HalpIsValidPCIDevice(), HalpSetPCIData(), and HalpValidPCISlot().

◆ HalpSetPCIData()

| ULONG NTAPI HalpSetPCIData | ( | IN PBUS_HANDLER | BusHandler, |

| IN PBUS_HANDLER | RootHandler, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 587 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), and HalSetBusDataByOffset().

◆ HalpValidPCISlot()

| BOOLEAN NTAPI HalpValidPCISlot | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot | ||

| ) |

Definition at line 329 of file pcibus.c.

Referenced by HalpReadPCIConfig(), and HalpWritePCIConfig().

◆ HalpWritePCIConfig()

| VOID NTAPI HalpWritePCIConfig | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 283 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), HalpAssignPCISlotResources(), HalpDebugPciDumpBus(), and HalpSetPCIData().

◆ PciSize()

Variable Documentation

◆ HalpBusType

| ULONG HalpBusType |

Definition at line 18 of file pcibus.c.

Referenced by HalHandleNMI(), HalInitSystem(), HalpInitDma(), HalpInitializeCmos(), HalpIs16BitPortDecodeSupported(), HalpRegisterInternalBusHandlers(), and HalReportResourceUsage().

◆ HalpFakePciBusData

| PCIPBUSDATA HalpFakePciBusData |

◆ HalpFakePciBusHandler

| BUS_HANDLER HalpFakePciBusHandler |

Definition at line 94 of file pcibus.c.

Referenced by HalGetBusDataByOffset(), HaliPciInterfaceReadConfig(), HalpAssignSlotResources(), HalpInitializePciStubs(), and HalSetBusDataByOffset().

◆ HalpMaxPciBus

| ULONG HalpMaxPciBus |

Definition at line 21 of file pcibus.c.

Referenced by HalpInitializePciStubs().

◆ HalpMinPciBus

| ULONG HalpMinPciBus |

Definition at line 21 of file pcibus.c.

Referenced by HalGetBusDataByOffset().

◆ HalpPCIConfigInitialized

| BOOLEAN HalpPCIConfigInitialized |

Definition at line 20 of file pcibus.c.

Referenced by HalGetBusDataByOffset(), HalpInitializePciStubs(), and HalSetBusDataByOffset().

◆ HalpPCIConfigLock

| KSPIN_LOCK HalpPCIConfigLock |

Definition at line 22 of file pcibus.c.

Referenced by HalpInitializePciBus(), HalpInitializePciStubs(), HalpPCIReleaseSynchronizationType2(), HalpPCIReleaseSynchronzationType1(), HalpPCISynchronizeType1(), and HalpPCISynchronizeType2().

◆ HalpPciLockSettings

|

extern |

Definition at line 20 of file halinit.c.

Referenced by HalpAdjustPCIResourceList(), and HalpGetParameters().

◆ PCIConfigHandler

| PCI_CONFIG_HANDLER PCIConfigHandler |

Definition at line 23 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), HalpInitializePciStubs(), HalpPCIConfig(), HalpReadPCIConfig(), and HalpWritePCIConfig().

◆ PCIConfigHandlerType1

| PCI_CONFIG_HANDLER PCIConfigHandlerType1 |

Definition at line 35 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), and HalpInitializePciStubs().

◆ PCIConfigHandlerType2

| PCI_CONFIG_HANDLER PCIConfigHandlerType2 |

Definition at line 57 of file pcibus.c.

Referenced by HalpAllocateAndInitPciBusHandler(), and HalpInitializePciStubs().

◆ PCIDeref

| UCHAR PCIDeref[4][4] |

Definition at line 26 of file pcibus.c.

Referenced by HalpPCIConfig(), HalpPhase0GetPciDataByOffset(), and HalpPhase0SetPciDataByOffset().